# P.A.C. RAMASAMY RAJA POLYTECHNIC COLLEGE, RAJAPALAYAM

# DEPARTMENT OF ELECTRICAL & ELECTRONICS ENGG.

## CENTRALIZED DOTE VALUATION - OCTOBER 2014

ANSWER KEY

Sub.Code : 25231

Qn.Code : 559

Sub.Name : Basics of Electrical and Electronics Engineering

Prepared By,

S.Narayanan Lecturer/EEE

checked

JEMMONUEL PAULRAJA JIZGIOOZ

BL/EEE, CSIPTC

### Answer Key October 2014

Subject: Basics of Electrical and

Subject Code: 25231

Electronics Engineering

1. State the equivalent resistance of two resistors R1 and R2 when connected in series.

Rs = R1 + R2

2. Define the term Energy.

Energy is defind as the ablity to work.

Electrical energy = power X time = Pt Whr

3. Define cycle.

One complete positive and one complete negative alternation of current or voltage is known as cycle

4. What is primary cell?

It is an electric cell that produces current by an irreversible chemical reaction.

5. What is auto transformer?

A transformer in which the primary and secondary coils have part or all of their turns in common. The primary voltage is applied across two of the terminals, and the secondary voltage taken from two terminals, almost always having one terminal in common with the primary voltage.

- 6. What are the different types of servo motor?

- 1. Brushless servo motor.

- 2. Permanent Magnet servo motor.

- 7. Name the different types of UPS.

- 1. On line UPS

- 2. Off line UPS

- 8. What is the need of fuse?

The need of fuse is to protect the devices from

- 1. Overcurrent

- 2. Overheat

- s. Short circuit

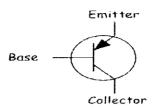

#### 9. Draw the symbol of PNP transistor.

#### 10. What is meant by doping?

The process of adding impurity to a semiconductor is known as DOPING.

#### 11. What are rectifiers?

A semiconductor device which converts of an alternating current (AC) into direct current (DC).

#### 12. Define ripple factor.

Ripple Factor: The ratio of r.m.s value of ac component to the dc component in the rectifier output is known as ripple factor.

Ripple Factor= r.m.s value of ac component/ value of dc component

#### 13. Expand ASCII and BCD

ASCII- American Standard Code for Information Interchange BCD - Binary Coded Decimal

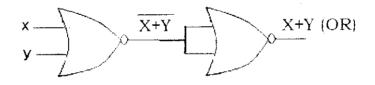

#### 14. Draw OR gate using NOR gate.

#### 15. Simplify ABD+ABD using Boolean laws and theorems.

$$\overrightarrow{ABD} + \overrightarrow{ABD} = \overrightarrow{AB} (D+D)$$

=  $\overrightarrow{AB}$  (Since,  $D+\overline{D}=1$ )

#### 16 What is multiplexer?

A multiplexer (or mux) is a device that selects one of several analog or digital input signals and forwards the selected input into a single line.

A multiplexer of 2n inputs has n select lines, which are used to select which input line to send to the output.

#### 17. Which flip flop is used to avoid racing?

The J-K flip flop should be used with edge triggered method in order to avoid racing.

#### 18. How many flip flops are needed to construct mod-18 counter?

There are 5 numbers of flip flops are required to design mod-18 counter.

#### 19. What is a shift register?

Shift register is a cascade of flip flop that is designed to allow the bits of its contents to be moved to left or right.

#### 20. Write the truth table of D-flip flop.

| elk | ٥  | Q        | $\overline{\mathbb{Q}}$ |

|-----|----|----------|-------------------------|

| 0   | () | G        | $\overline{\Omega}$     |

| Ō   | 1  | a        | Q                       |

| 1   | 0  | 0        | 1                       |

| 1   | 1  | <u>*</u> | 0                       |

# 21.A.i. Define the following terms: Resistance, current, Power and Potential difference. $4 \times 2 = 8 \text{ Manks}$

## Resistance: (2 Marks)

It is defined as the property of a material, which opposes the flow of current in it. Due to this property; the material dissipates heat energy while current flows through it. It is denoted by the letter 'R'. The practical unit of resistance is ohm  $(\Omega)$

## Electric current: (2 Marks)

The rate of flow of electric charges is called, "electric current". The unit of current is ampere (A). It is denoted by the letter 'I'

Current =

$$\frac{Charges}{Time}$$

(i.e.)  $I = \frac{Q}{t}$

#### Power: (2 Manks)

It is defined as the product of Voltage and Current flows through the circuit. The unit of power is watt. Three forms power can be written as follows,

$$P = V * I$$

$$P = V^{2} / R$$

$$P = I^{2} * R$$

## Potential difference: (P.D) (2 Marks)

The voltage measured across the source terminal is called as EMF and when it is measured at the load terminal, it is called as potential difference or terminal voltage (V). EMF and potential difference are measured in volts.

# 21.A.ii. What are the advantages of AC over DC? [Any Four Point has one mank]

- 1) Most of the advantages of A.C. over D.C are related to power transmission over long distances.

- 2) A.C. power can be transmitted at extremely high voltages. By using a transformer, changed into the required voltage by the device at the user end (including changing A.C. into D.C. if required).

- 3) These two facts mean that you can have fewer, larger power stations located further away from the user; whereas with D.C. you must have many smaller power stations located close to the user.

- 4) It can have least loss power loss due to heating.

- 5) It is easier and cheaper to produce.

5

#### Care and Maintenance of lead acid battery.

The quickest way to ruin lead-acid batteries is to discharge them deeply and leave them stand "dead" for an extended period of time. When they discharge, there is a chemical change in the positive plates of the battery.

They change from lead oxide when charged to lead sulfate when discharged. If they remain in the lead sulfate state for a few days, some part of the plate does not return to lead oxide when the battery is recharged. If the battery remains discharged longer, a greater amount of the positive plate will remain lead sulfate. The parts of the plates that become "sulfated" no longer store energy. Batteries that are deeply discharged, and then charged partially on a regular basis can fail in less than one year.

Check your batteries on a regular basis to be sure they are getting charged. Use a hydrometer to check the specific gravity of your lead acid batteries. If batteries are cycled very deeply and then recharged quickly, the specific gravity reading will be lower than it should because the electrolyte at the top of the battery may not have mixed with the "charged" electrolyte.

Check the electrolyte level in wet-cell batteries at least four times a year and top each cell off with distilled water. Do not add water to discharged batteries. Electrolyte is absorbed when batteries are very discharged. If you add water at this time, and then recharge the battery, electrolyte will overflow and make a mess.

Keep the tops of your batteries clean and check that cables are tight. Do not tighten or remove cables while charging or discharging. Any spark around batteries can cause a hydrogen explosion inside, and ruin one of the cells, and you.

It is a good idea to do an equalizing charge when some cells show a variation of 0.05 specific gravity from each other. This is a long steady overcharge, bringing the battery to a gassing or bubbling state. Do not equalize sealed or gel type batteries.

With proper care, lead-acid batteries will have a long service life and work very well in almost any power system. Unfortunately, with poor treatment lead-acid battery life will be very short.

#### Cautions:

1. Keep batteries in place, where children can not reach.

- 2. Do not attempt to disassemble, revise, damage, impact, dispose batteries, otherwise the battery can leak, be overheated, or explore.

- 3. Do not dispose of the batteries in water, fire, and do not heating the batteries.

- 4. Do not short batteries.

- 5. Do not put your face near the top of batteries. Please wear gloves, eye protection when you measure or repair batteries.

- 6. There is sulfuric acid in the battery. Do not make contact with sulfuric acid in skin, clothes, or especially in eyes. If eyes make contact with sulfuric acid, please wash with a lot of clean water, and consult a physician immediately.

- 7. The suitable temperature is -15-+50, but it will have longer life in the temperature from +20-+30. The operation circumstances and defined as: discharging temperature range -15-+50; charging temperature range 0-+40.

## 22.A.i. Explain the basic principle of operation of a transformer.

Others-4 marks

#### Transformer

Electrical power transformer is a static device which transforms electrical energy from one circuit to another without any direct electrical connection and with the help of mutual induction between two windings. It transforms power from one circuit to another without changing its frequency but may be in different voltage level.

#### **Working Principle of Transformer**

The working principle of transformer is very simple. It depends upon Faraday's law of electromagnetic induction. Actually, mutual induction between two or more winding is responsible for transformation action in an electrical transformer.

# Faraday's Laws of Electromagnetic Induction ( & Marks)

According to these Faraday's laws, (Law Statement: 2 marks)

"Rate of change of flux linkage with respect to time is directly proportional to the induced EMF in a conductor or coil".

#### Principle:

Primary winding which is supplied by an alternating electrical source. The alternating current through the winding produces a continually changing flux or alternating flux that surrounds the winding. If any other winding (Secondary)is brought nearer to the previous one, obviously some portion of this flux will link with the second. As this flux is continually changing in its amplitude and direction, there must be a change in flux linkage in the second winding or coil. According to Faraday's law of electromagnetic induction, there must be an EMF induced in the second. If the circuit of the later winding is closed, there must be an current flowing through it. This is the simplest form of electrical power transformer and this is the most basic of working principle of transformer.

#### 22.A.ii. Explain the specification and rating of UPS.

(4)

#### Rating and Specification of UPS.

Any Four points, each one carries one marily

| Type of input          | KVA              | Max.Current      |

|------------------------|------------------|------------------|

| Single phase input UPS | 8.0 KVA-10.0 KVA | 43.4 A to 54.3 A |

| Three phase input UPS  | >10 KVA          | 54.3A            |

Voltage The input voltage specification is the nominal voltage

the UPS expects to see on its input.

Voltage All UPS products range of input vol

All UPS products are designed to operate over a range of input voltages. A typical range is +10% to -

15%.

Frequency Modern UPS equipment will operate on either 50 or

60Hz as long as the voltage is within the specified

limits. Some UPS equipment is designed to operate only on 50 or 60Hz.

#### Maximum Current

The maximum current occurs when the UPS is fully loaded and the input voltage is at the minimum allowed for normal operation (usually about -15%).

#### **Power Factor**

The UPS input is a load on the utility power source. The UPS input power factor (p.f.) varies with how much load is on the output. In large UPS equipment (e.g. 25kVA) the input power factor could be a very important part of the overall system design.

(or)

#### What are the precautions to be taken to avoid electric shock? ( dny 10 Points = 12 Marks) 22.B

There are various ways of protecting people from the hazards caused by electricity, including insulation, guarding, grounding, and electrical protective devices.

Minimize the potential for water or chemical spills on or near electrical equipment.

#### Insulation

All electrical cords should have sufficient insulation to prevent direct contact with wires.

Damaged cords should be repaired or taken out of service immediately, especially in wet environments such as cold rooms and near water baths

#### Guarding

Live parts of electric equipment operating at 50 volts or more (i.e., electrophoresis devices) must be guarded against accidental contact. Plexiglas shields may be used to protect against exposed live parts

#### Grounding

Only equipment with three-prong plugs should be used. The third prong provides a path to ground that helps prevent the build up of voltages that may result in an electrical shock or spark.

This does not guarantee that no one will receive a shock, be injured, or be killed. It will, however, substantially reduce the possibility of such accidents, especially when used in combination with other safety measures.

#### **Protecting Devices:**

By using protective devices which are designed to automatically limit or shut off the flow of electricity in the event of a fault. Some of the examples are,

Circuit breaker

- 2. Fuse

- 3. Relays etc.,

# Workers can significantly reduce electrical hazards by following some basic precautions:

- 1. Inspect wiring of equipment before each use. Replace damaged or frayed electrical cords immediately.

- 2. Use safe work practices every time electrical equipment is used. Know the location and how to operate shut-off switches and/or circuit breaker panels. Use these devices to shut off equipment in the event of a fire or electrocution.

- 3. Limit the use of extension cords. Use only for temporary operations. In all other cases, request installation of a new electrical outlet.

- 4. Use only multi-plug adapters equipped with circuit breakers or fuses.

- 5. Place exposed electrical conductors (such as those sometimes used with electrophoresis devices) behind Plexiglas shields.

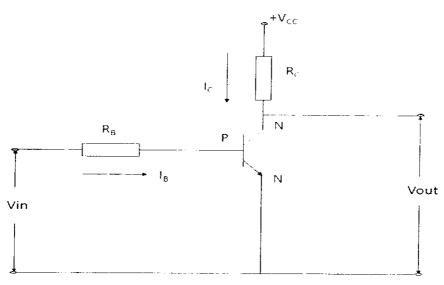

#### Transistor as a switch:

The transistor as a switch operates between two states namely saturation and cut off state. The typical transistor circuit is shown in figure. It consist of a transistor with collector load resistance Rc. The input is given at base terminal and output is taken at collector terminal.

When the input signal is negative, the emitter base junction will reverse biased and the transistor never comes to conduction state. The transistor will be in cut off and no current flows in the load resistance Rc. As a result there is no voltage drop across Rc.

Figure: Transistor as a switch

Hence the output voltage will be supply voltage i.e. Vo= Vcc. It is equal to open circuit voltage since the transistor is in cut off.

When the input voltage is positive, it forward biases the base-emitter junction and the transistor will come to conduction state. Now maximum current will be flowing from collector to emitter and all the Vcc is dropped across Rc. Thus the output voltage will be zero. i.e. Vo=0

Hence the transistor is tuned on and off depending upon whether the input bias voltage is positive or negative. Thus a transistor can act as a switch.

#### 23.A.ii.

# Write shorts notes on p type and N type semiconductor. Spryke-3 marks [6] Extrinsic semiconductors: When a suitable metallic imposite is all 1

When a suitable metallic impurity is added to an intrinsic (pure) semiconductor. It is called an extrinsic semiconductor.

An intrinsic semiconductor behaves as an insulator at room temperature however, if some suitable metallic impurity is added to an intrinsic semiconductor, the extrinsic semiconductor thus obtained shows current conducting properties even at room temperature.

The process of adding impurity to a semiconductor is known as DOPING.

Depending upon the type of impurity added, the extrinsic semiconductors are divided into the following two types:

- 1. N-type semiconductor

- 2. P-type semiconductor

#### N-TYPE SEMICONDUCTOR:

When a small amount of pentavalent impurity is added to a pure semiconductor, it is known as N-type semi conductor. Typical examples are pentavalent impurities arsenic, antimony, and phosphorus. Such impurities, which produce N-type semiconductors, are known as donor impurities because these provide or donate excess electrons in the semiconductor crystal.

#### P-TYPE SEMICONDUCTOR:

When a small amount of trivalent impurity is added to a pure semiconductor, it is known as P-type semiconductor. Typical examples are trivalent impurities like aluminium, gallium, and indium. Such impurities are called acceptor impurities. They are so, called because the holes created can accept electrons.

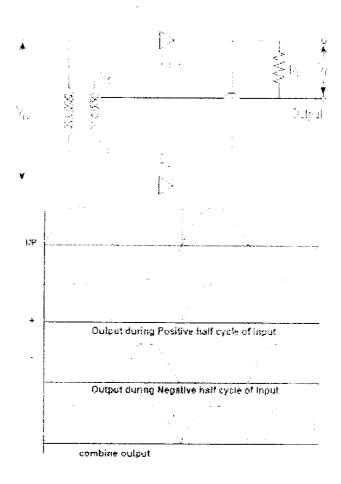

23.B. Explain the operation of full wave rectifier and draw its input and output (12) waveforms.

Diagram and Waveform - 6 Marks

Operation - 6 Marks

#### Full Wave Rectifier:

A full wave rectifier is an electronic circuit, which converts A.C voltage into a pulsating D.C voltage using both half cycles of the applied A.C input voltage.

#### Construction:

It consists of a transformer, two semiconductor diodes and a load resistor  $R_L$ . The secondary winding of the transformer is centre tapped. Hence the two voltages  $V_1$  and  $V_2$  fed to the two diodes are equal in magnitude but opposite in  $180^\circ$  phase difference. One end terminal (A) of the transformer secondary is connected to the anode of diode  $D_1$  and the other end terminal (B) is connected to the anode of diode  $D_2$ . The load resistor RL is connected between the centre tap C of the secondary winding and inter junction of two cathodes of diode  $D_1$  and  $D_2$ .

Fig. shows the basic circuit of a full wave rectifier.

#### Working:

When an A.C voltage is applied to the input circuit, the end terminals A and B of the transformer secondary becomes positive and negative alternately. During positive half cycle of the A.C input voltage, terminal A is at positive

potential, C is at zero potential and B is at negative potential. This makes the anode of the diode D1 positive with respect to cathode. Now the diode D1 is forward biased and D2 is reverse biased. Therefore the diode D1 conducts and at the same time diode D2 remains non-conducting. A current I1 flows through the load resistance RL in the direction as shown in fig.

During the negative half cycle of the A.C input voltage, terminal A is at negative potential, C is at zero potential and B is at positive potential. This makes the anode of the diode D2 positive with respect to cathode. Now the diode D2 is forward biased and D1 is reverse biased. Therefore the diode D2 conducts and diode D1 remains non-conducting. A current I2 flows through the load resistor Rl in the directions as shown in fig.

Thus when an A.C voltage is applied to the full wave rectifier, during positive half cycle diode D<sub>1</sub> conducts and during the negative half cycle diode D<sub>2</sub> conducts. Further, current flows through the load resistor R<sub>L</sub> in the same direction in both half cycles of the A.C input. A pulsating D.C voltage is developed across the load resistor R<sub>L</sub>. The input and output waveforms are shown in fig.

#### Advantages:

High output voltage, than half wave rectifier  $V_{dc} = 0.637 V_{m}$ . Rectification efficiency is high = 81.2%.

- 3. Ripple factor is low = 0.421.

- 4. D.C saturation of the core is avoided.

(Since equal currents flow through the two halves of the centre tapped secondary of the power transformer in opposite direction).

#### Disadvantages:

Cost is high, when compared to half wave rectifiers.

Requires centre tapped transformer, which is more costly.

Higher PIV rated diodes are necessary for the operation, which increases the Write short notes on ASCII Code. Others & Marks ]

#### 24.A.i.

ASCII- (American Standard Code for Information Interchange) is the most widely used coding system to represent data.

ASCII is used on many personal computers and minicomputers. ASCII is a 7-bit code that permits 27=128 distinct characters.

The 128 different combinations that can be represented in 7 bits are plenty to allow for all the letters, numbers and special symbols. An eight bit was added. This allowed extra 128 characters to be represented. The extra 128 combinations are used for symbols such as Ç ü è ©, ®, Æ, etc.

The codes for the alphabetical characters indicate their relative positions in the alphabet in ASCII. This is known as collating sequence, thus, sorting textual items can be transformed into sorting the corresponding character codes. Also, in ASCII, uppercase characters, lowercase characters and digits etc, are grouped together. So it is easy to map between upper and lower case characters.

(4)

The characters with codes 0 through 31 are known as *control characters* (because historically they were used to control teletype operations). They are referred to by their abbreviations (CR for carriage return, LF for linefeed, ESC for escape, and so on) or by the word "Ctrl" followed by a corresponding letter (meaning the letter produced by adding 64 to the control code). For example, the control character with ASCII code 7 is known as BEL or Ctrl-G

# 24.A.ii. Write the truth table, logical equation and symbols of 2 inputs (8) AND,OR,XOR and NAND gates. Fach gate 2 Monks; 4 x 2 : 8 Monks

#### Logic Gates

Logic gates are electronic circuits, which are used to make logic decisions.

Logic gates may have one or more inputs and one output. Logic gates are the building blocks of digital systems.

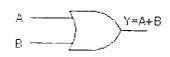

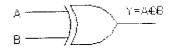

#### OR Gate:

In a two input OR gate, the output will be at High level, if one of the inputs or both the inputs are at High level.

|   | INP | UTS | OUTPUT                                 |  |  |

|---|-----|-----|----------------------------------------|--|--|

|   | A   | В   | $\mathbf{A} = \mathbf{V} + \mathbf{B}$ |  |  |

| - | 0   | 0   | 0                                      |  |  |

| - | 0   | 1   | 1                                      |  |  |

|   | 1   | 0   | 1                                      |  |  |

|   | 1   | 1   | 1                                      |  |  |

Fig 1.1 Truth table and logic symbol of OR gate

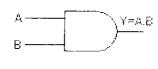

#### AND gate:

In a two input AND gate, the output will be at High level, if both the inputs A and B are at High level.

| INF | PUTS | OUTPUT  |

|-----|------|---------|

| A   | В    | Y = A.B |

| 0   | 0    | 0       |

| 0   | 1    | 0       |

| 1   | 0    | 0       |

| 1   | 1    | 1       |

Fig 1.2 Truth table and logic symbol of And gate

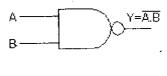

#### **NAND Gate:**

It is a combination of NOT gate and AND gates. In a two input NAND gate, the output will be at High level, if input A or input B or inputs A and B are at Low level.

| INP | UTS | OUTPUT               |

|-----|-----|----------------------|

| A   | В   | $Y = \overline{A.B}$ |

| 0   | 0   | 1                    |

| 0   | 1   | 1                    |

| 1   | 0   | 1                    |

| 1   | 1   | 0                    |

|     |     |                      |

Fig 1.5 Truth table and logic symbol of NAND gate

#### Exclusive OR gate (EX-OR / X-OR):

In a two input Ex-OR gate, the output will be at High level, if the inputs are at different levels.

| INF | PUTS | OUTPUT           |

|-----|------|------------------|

| A   | В    | $Y = A \oplus B$ |

| 0   | 0    | 0                |

| 0   | 1    | 1                |

| 1   | 0    | 1                |

| 1   | 1    | 0                |

| 1   | 1    |                  |

Touth table

Fig 1.6 Truth table and logic symbol of Ex-OR gate

(or)

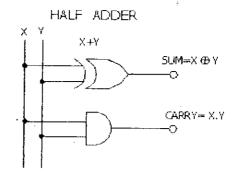

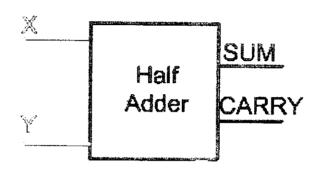

#### Draw the logic diagram and give the truth table and logical equations for (6) 24.B.i. logic diagram - 2 magice half adder.

**Half Adder:**

Half adder is used to add two bits at a time. The outputs of the adder are carry bit and sum bit. The truth table of a half adder is shown in Fig(a). Its construction using gates is shown in Fig (b).

| INPUTS |   | OUTPUTS |     |  |

|--------|---|---------|-----|--|

| X      | Y | CARRY   | SUM |  |

| 0      | 0 | 0       | 0   |  |

| 0      | 1 | 0       | 1   |  |

| 1      | 0 | 0       | 1   |  |

| 1      | 1 | 1       | 0   |  |

Fig (a) Half Adder-Truth Table

Fig 2.1 (b) Half Adder-Construction using gates

Block Diagram:

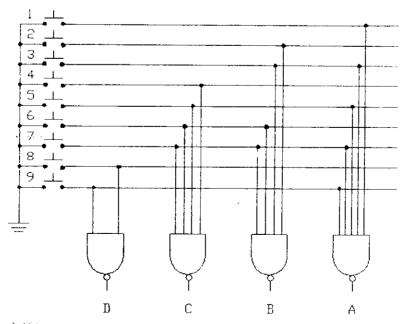

# 24B.ii. Explain the working of encoder. Encoders:

Diagram - 3 marky others - 3 marky

Encoding of information is the reverse process of decoding. It can be used for converting decimal number into binary to feed it into a digital system. An encoder for converting decimal number to binary is shown in Fig 2.15.

Four Nand gates are employed in this encoder. When a switch is pressed (i.e. grounded), inputs of the Nand gates connected to this switch go Low and their

(6)

output(s) go High and the outputs of other Nand gates go Low. If switch 6 is pressed, one of the inputs of two Nand gates go Low and  $Q_B$  and  $Q_C$  go High. As the other two Nand gates are not connected to this switch, their outputs are at Low level i.e.  $Q_DQ_CQ_BQ_A = 0110$ , which is the binary equivalent for  $\theta_{10}$ .

#### 25.A.i. Explain the working of JK flip flop.

Diagram - 2 Marks Others - 4 marks

(6)

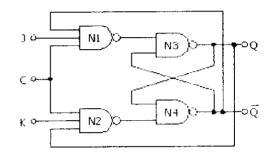

#### JK flip-flop

In SR flip-flop S=R=1 is a forbidden state. JK flip-flop eliminates the forbidden state. Here when J=K=1, the output *toggles*, i.e. its changes its output state for each input pulse. A JK flip-flop using Nand gates is shown in Fig 4.6.

It has three inputs namely J and K inputs and the clock. Nand gate N1 has three inputs, the clock, J input and the output from Q. Nand gate N2 has three inputs, the clock, K input and the feedback from Q. Four cases are possible.

Fig 4.6 JK flip-flop using Nand gates

#### Case: 1 Let J=High and K=Low

Let us assume that initially Q is Low and Q is High. When the clock and J inputs are High, all the inputs to N1 are High. Output of N1 hence is Low. As one input to N3 is Low its output goes High i.e. Q is made High. As N2 has at least one input K (and also Q) Low, N2 output goes High. This makes  $\overline{Q}$  to go Low. This is the Set condition.

#### Case: 2 Let J=Low and K=High

Let us assume that initially Q is High and  $\overline{Q}$  is Low. When the clock and K inputs are High, all inputs to N2 are High. Its output goes Low. As the input to N4 is Low, its output i.e.  $\overline{Q}$  goes High. As J=0, N1 output goes High. Hence Q goes Low. This is the Reset condition.

#### Case: 3 Let J=K=Low

Even if the clock is present, output remains in its old state.

#### Case: 4 Let J=K=High

Let us assume that Q is Low and Q is High initially. As seen in case: 1, Q goes High and  $\overline{Q}$  goes Low when a clock pulse strikes the flip-flop. The next clock pulse will make Q to go Low and  $\overline{Q}$  to go High as explained in case 2. This shows that the output changes state whenever a clock pulse strikes the flip-flop. The change of output state (of Q and  $\overline{Q}$ ) for every input pulse is called *toggling*.

|   | ,     |   | Tr | uth T | able of   | f JK flip-flop |

|---|-------|---|----|-------|-----------|----------------|

|   | Clock | J | K  | Qn    | $Q_{n+1}$ |                |

|   | 0     | X | X  | Qn    | Qn        | No change      |

| ļ | 1     | 0 | 0  | 0     | 0 ·       | No change      |

|   |       | 0 | 0  | 1     | 1         |                |

|   | 1     | 0 | 1  | 0     | 0         | Reset          |

|       | 1        | 0       | 0    | 0      | 0 . | No change      |

|-------|----------|---------|------|--------|-----|----------------|

|       | reter .  | 0       | О    | 1      | 1   |                |

|       | 1        | 0       | 1    | 0      | 0   | Reset          |

|       |          | 0       | 1    | 1      | 0   |                |

|       | 1        | 1       | 0    | 0      | 1   | Set            |

|       |          | 1       | 0    | 1      | 1   |                |

|       | 1        | 1       | 1    | 0      | 1   | Toggle state   |

|       | · ·      | 1       | 1    | 1      | 0   |                |

| $f_i$ | or the . | IK flin | flon | is she |     | TS - 4.77 1.11 |

The symbol for the JK flip-flop is shown in Fig 4.7 and the truth table in Table.

**Race around condition:** The output is feedback to the input and therefore changes in the output results change the input. Due to this in the positive half of the clock pulse if J and K are both high then output toggles continuously.

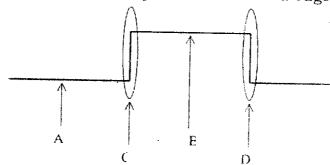

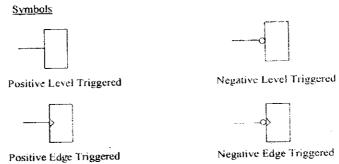

# 25.A.ii. Explain triggering of flip flops. Triggering & Clocking

(6 Marks)

(6)

A trigger is a control signal used to initiate an action.

In the gated latches, the trigger is the enable line. Setting the enable HIGH allows the latch to be set or reset.

Triggers can be of two forms

- 1. Level Triggers (HIGH or LOW levels)

- 2. Edge Triggers (+ve or -ve going transitions)

Examining a pulse, indicates all the possible levels and edges

| Letter | Comment                                                                       |

|--------|-------------------------------------------------------------------------------|

| A      | LOW level                                                                     |

| В      | HIGH level                                                                    |

| C      | Positive Edge (LOW -> HIGH Transition)                                        |

| D      | Positive Edge (LOW -> HIGH Transition) Negative Edge (HIGH -> LOW Transition) |

A *level trigger* means that an action is initiated on either a LOW or HIGH level.

An *edge trigger* means that an action is initiated on either a positive or negative transition.

A clock is a series of pulses (Square Waves) used to synchronise actions. Generally the triggers are taken from the edges of the clock.

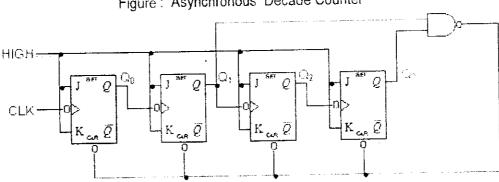

# 25.B. Explain decade counter with a block diagram, truth table and waveform.

The binary counters previously introduced have two to the power n states. But counters with states less than this number are also possible. They are designed to have the number of states in their sequences, which are called **truncated sequences**. These sequences are achived by forcing the counter to recycle before going through all of its normal states.

A common modulus for counters with truncated sequences is ten. A counter with ten states in its sequence is called a **decade counter**. The circuit below is an implementation of a decade counter.

Truth table - 2 Minks

Wave form - 2 Manks

Others - 1 Manks

Once the counter counts to ten (1010) all the flip flops are being cleared. Notice that only Q1 and Q3 are used to decode the count of ten. This is called partial decoding, as none of the other states (zero to time) have both Q1 and Q3 HIGH at the same time.

10

The sequence and waveform of the decade counter is shown in below.

| Clock Pulse | 03 | Q2 | Q1 | QÜ  | 7   |

|-------------|----|----|----|-----|-----|

| 0           | 0  | Ō  | 0  | 0   | 1 € |

| 1           | .0 | 0  | 0  | 1 1 | 1   |

| 2           | 0  | ٥  | 1  | 0   | 1   |

| <u>_</u>    | 0  | 0  | 1  | 1   | 1   |

| 4           | 0  | 1  | 0  | 0   | 1   |

| 5           | 0  | 1  | 0  | 1   | 1   |

| 6           | 0  | 1  | 1  | Û   |     |

|             | 0  | 17 | 1  | 1   |     |

| 8 1         | 1  | 0  | Ô  | Ū   |     |

| 9           | 1  | 0  | 0  | 1   |     |

Figure True Table Asynchronous Decade Counter

# Waveforms

| COUNT      | 11日日日日日日日日日日 |

|------------|--------------|

| <b>Q</b> 0 |              |

| $Q_1$      |              |

| $A_2$      |              |

| $A_3$      |              |

Prepared by,

S.Narayanan

Lecturer / EEE

P.A.C.R Polytechnic College, Rajapalayam.